RESSORTFORSCHUNGSBERICHTE ZUR SICHERHEIT DER NUKLEAREN ENTSORGUNG

# Analyse der Fehlermodi von programmierbaren logischen Schaltungen in der Sicherheitsleittechnik von Kernkraftwerken

Vorhaben FKZ 7420R01310

AUFTRAGNEHMER: INNEN:

TÜV Rheinland Industrie Service GmbH, Hallbergmoos

Berit Rauscher Dr. Marika Vespa Stephan Kistinger Kirsten Haneke

# Analyse der Fehlermodi von programmierbaren logischen Schaltungen in der Sicherheitsleittechnik von Kernkraftwerken

Dieser Band enthält einen Ergebnisbericht eines vom Bundesamt für die Sicherheit der nuklearen Entsorgung im Rahmen der Ressortforschung des BMU (ReFoPlan) in Auftrag gegebenen Untersuchungsvorhabens. Verantwortlich für den Inhalt sind allein die Autor:innen. Das BASE übernimmt keine Gewähr für die Richtigkeit, die Genauigkeit und Vollständigkeit der Angaben sowie die Beachtung privater Rechte Dritter. Der Auftraggeber behält sich alle Rechte vor. Insbesondere darf dieser Bericht nur mit seiner Zustimmung ganz oder teilweise vervielfältigt werden.

Der Bericht gibt die Auffassung und Meinung der Auftragnehmer:innen wieder und muss nicht mit der des BASE übereinstimmen.

#### BASE-RESFOR-028/24

Bitte beziehen Sie sich beim Zitieren dieses Dokumentes immer auf folgende URN: urn:nbn:de:0221-2024103048058

Berlin, November 2023

#### **Impressum**

Bundesamt für die Sicherheit der nuklearen Entsorgung (BASE)

RESSORTFORSCHUNGSBERICHTE ZUR SICHERHEIT DER NUKLEAREN ENTSORGUNG

#### Auftragnehmer:innen:

TÜV Rheinland Industrie Service GmbH, Hallbergmoos

Berit Rauscher Dr. Marika Vespa Stephan Kistinger Kirsten Haneke

030 184321-0 www.base.bund.de

Stand: November 2023

GZ: A 1 - BASE - BASE23103/4721E03230#0004

# Analyse der Fehlermodi von programmierbaren logischen Schaltungen in der Sicherheitsleittechnik von Kernkraftwerken

#### **Abschlussbericht**

- R. Heigl

- H. Miedl

- G. Savchyn

- G. Schnürer

- D. Wölbing

ISTec - A - 4013

Rev. 5.0

November 2023

Das diesem Bericht zugrundeliegende F&E-Vorhaben wurde im Auftrag des Bundesministeriums für Umwelt, Naturschutz und nukleare Sicherheit unter dem Kennzeichen 7420R01310 durchgeführt. Der Bericht gibt die Auffassung und Meinung des Auftragnehmers wieder und muss nicht mit der Meinung der Auftraggeberin übereinstimmen.

# **INHALTSVERZEICHNIS**

| Kurzfas | sung                                                                                       | 1           |

|---------|--------------------------------------------------------------------------------------------|-------------|

| Abstrac | xt                                                                                         | 2           |

| 1       | Einleitung                                                                                 | 3           |

| 1.1     | Beauftragung                                                                               | 3           |

| 1.2     | Zielsetzung                                                                                | 3           |

| 1.3     | Technologien                                                                               | 4           |

| 2       | Begriffe und Abkürzungen                                                                   | 7           |

| 2.1     | Begriffe                                                                                   | 7           |

| 2.2     | Abkürzungen                                                                                | 11          |

| 3       | Stand von Wissenschaft und Technik zum Fehlerpotential und zu Fehlermodi b<br>FPGA-Designs | oei<br>13   |

| 3.1     | Fehlermodi bei integrierter digitaler Leittechnik                                          | 14          |

| 3.2     | Fehlermodi im Zusammenhang mit modellbasierten FPGA-Entwicklungswerkze                     | eugen<br>16 |

| 3.3     | Testen von FPGA-Designs                                                                    | 18          |

| 3.4     | Vorangegangene eigene Projekte                                                             | 22          |

| 4       | Erstellung von FPGA-Designs zur Untersuchung der Fehlermodi                                | 26          |

| 4.1     | Werkzeugauswahl zur Erstellung und Prüfung von FPGA-Designs                                | 26          |

| 4.1.1   | Gemeinsamkeiten der gängigsten Entwicklungswerkzeuge                                       | 27          |

| 4.1.2   | Actel Libero IDE                                                                           | 27          |

| 4.1.3   | Altera Quartus                                                                             | 28          |

| 4.1.4   | Vivado Design Suite (Neuimplementierung der ISE Design Suite)                              | 28          |

| 4.1.5   | Auswahl der Vivado Design Suite                                                            | 28          |

| 4.2     | Spezifikation und Realisierung von FPGA-Designs                                            | 29          |

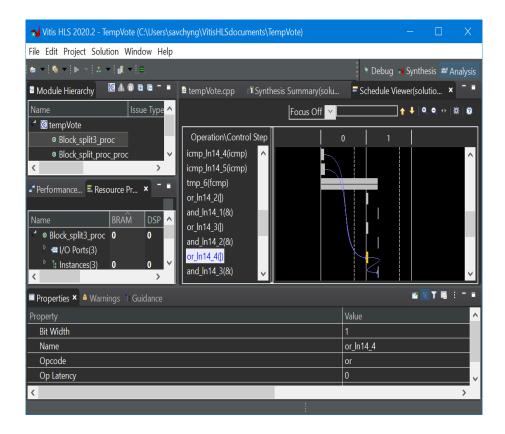

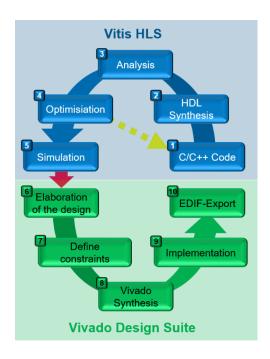

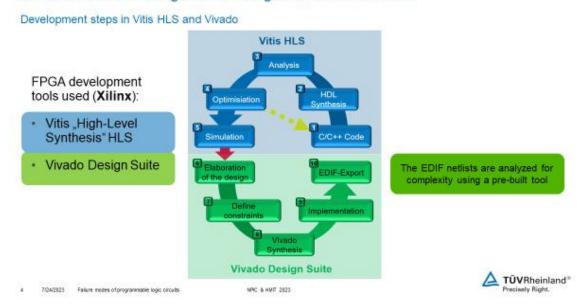

| 4.3     | FPGA-Entwicklung mittels Vitis HLS                                                         | 30          |

| 4.3.1   | C/C++ Code                                                                                 | 31          |

| 4.3.2   | HDL Synthese                                                                               | 32          |

| 4.3.3   | Analyse                                                                                    | 32          |

| 4.3.4   | Optimierung                                                                                | 33          |

| 4.3.5   | Simulation und Export                                                                      | 33          |

| 4.4     | Entwicklung mittels Vivado Design Suite                                                    | 35          |

| 4.4.1   | Elaborieren des Entwurfs                                                                   | 36          |

| 4.4.2   | Festlegung von Einschränkungen                                                             | 37          |

| 4.4.3   | Synthese in Vivado                                                                         | 38          |

|         |                                                                                            |             |

| Fehlerm | odi programmierbarer logischer Schaltungen – Abschlussbericht                  | HS        |

|---------|--------------------------------------------------------------------------------|-----------|

| 4.4.4   | Platzierung                                                                    | 38        |

| 4.4.5   | EDIF                                                                           | 39        |

| 4.5     | Realisierung der FPGA-Designs                                                  | 39        |

| 4.5.1   | Eingangsprüfung                                                                | 39        |

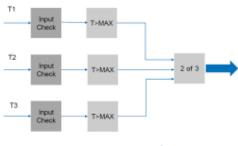

| 4.5.2   | 2-von-3-Auswahlschaltung                                                       | 41        |

| 4.5.3   | Redundanzschaltung                                                             | 43        |

| 4.6     | Erstellung einer geeigneten Testumgebung                                       | 46        |

| 4.6.1   | Testplan                                                                       | 46        |

| 4.6.2   | Dynamische Codeanalyse                                                         | 47        |

| 4.6.3   | Bestimmung der zyklomatischen Komplexität des Codes                            | 49        |

| 4.6.4   | Diversitätstest                                                                | 50        |

| 4.6.5   | Erstellung und Vergleich der Wellenfunktionen auf verschiedenen Betriebssyster | men<br>50 |

| 4.6.6   | Tests mit einem diversitären Compiler                                          | 51        |

| 4.6.7   | Diversitäres Synthese-Werkzeug                                                 | 51        |

| 4.6.8   | Diversitärer Testbanksimulator (Altera ModelSim)                               | 51        |

| 5       | Analyse der Fehlermodi mittels Testumgebung                                    | 52        |

| 5.1     | Mögliche Designschwächen bei der Entwicklung                                   | 52        |

| 5.1.1   | Fehler bei der Berechnung mit Konstanten und Variablen                         | 52        |

| 5.1.2   | Variablendoppelbelegung                                                        | 53        |

| 5.1.3   | Logikfehler einer bedingten Anweisung - Vergleichszeichen Fehler               | 53        |

| 5.1.4   | Falsche Festlegung von Grenzwerten                                             | 53        |

| 5.1.5   | Syntaxfehler im C bzw. C++ Code                                                | 54        |

| 5.1.6   | Vermengung der Dezimalstellenkonvention                                        | 54        |

| 5.1.7   | Fehler bei Definition der Variablen und Rundungen                              | 54        |

| 5.1.8   | Werkzeugbasierte Fehler                                                        | 55        |

| 5.1.9   | Auswirkungen von Strahlung auf FPGAs                                           | 55        |

| 5.2     | Testmethoden                                                                   | 56        |

| 5.2.1   | C-Simulation                                                                   | 56        |

| 5.2.2   | Analyse des HDL-Designs                                                        | 57        |

| 5.2.3   | C/RTL Co-Simulation                                                            | 58        |

| 5.2.4   | Wellenfunktion                                                                 | 58        |

| 5.2.5   | Vivado-Simulation                                                              | 59        |

| 5.2.6   | Vivado-Analysen                                                                | 59        |

|         |                                                                                |           |

| Fehlermo | odi programmierbarer logischer Schaltungen – Abschlussbericht                                                 | TIS |

|----------|---------------------------------------------------------------------------------------------------------------|-----|

| 5.3      | Ermittlung von Schwachstellen und potenziellen Fehlerquellen                                                  | 61  |

| 5.4      | Fehlerinjektion postulierter Fehler                                                                           | 63  |

| 5.4.1    | Sensorausfall                                                                                                 | 63  |

| 5.4.2    | Eingabe von unzulässigen Werten                                                                               | 64  |

| 5.4.3    | Variablen Doppelbelegung zur Identifikation von Konflikten zwischen Quellcode und Hardware (Codemanipulation) | 65  |

| 5.4.4    | Syntax und Semantik Fehler (Codemanipulation)                                                                 | 66  |

| 5.4.5    | Manipulation bei der Grenzwertanpassung (Codemanipulation)                                                    | 66  |

| 5.4.6    | Manipulation der Präzision der Eingabewerte der Sensoren                                                      | 67  |

| 5.4.7    | Syntaxfehler bei der Eingabe - Ersetzen von "Punkt" durch "Komma"                                             | 68  |

| 5.4.8    | Auswertung der Testschritte zur Fehlerinjektion                                                               | 69  |

| 5.4.9    | Fehlerinjektion in der Literatur (VTT Modell)                                                                 | 70  |

| 6        | Analyse der Komplexität von FPGA Designs                                                                      | 71  |

| 6.1      | Bestimmung der Komplexität                                                                                    | 71  |

| 6.2      | Berücksichtigung der Komplexität zur Generierung von Testfällen                                               | 73  |

| 6.3      | Untersuchung der Auswirkung von Änderungen auf die Komplexität von FPGA-Anwendungen                           | 75  |

| 7        | Potenzielle Kriterien für die Qualifizierung von programmierbarer Logik                                       | 77  |

| 8        | Zusammenfassung                                                                                               | 80  |

| 9        | Referenzen                                                                                                    | 83  |

| Anhang   | A ISTec-A-4010, Teilbericht                                                                                   | 88  |

| Anhang   | B Publikation NPIC&HMIT                                                                                       | 89  |

| Anhang   | C PowerPoint Folien zum Vortrag der TIS zur NPIC                                                              | 101 |

# **ABBILDUNGSVERZEICHNIS**

| Abbildung 1: Architekturtypen von programmierbarer Logik [1]                                                              |

|---------------------------------------------------------------------------------------------------------------------------|

| Abbildung 2: Entwicklungslebenszyklus programmierbarer logischer Schaltungen (HPD) [4]18                                  |

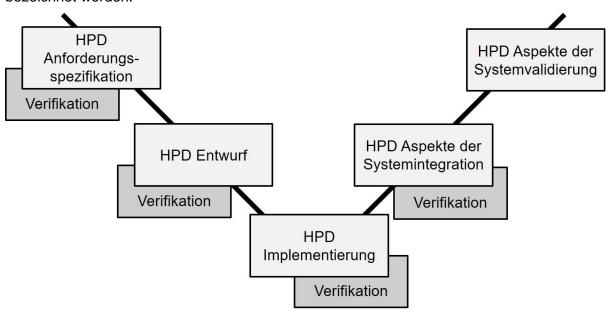

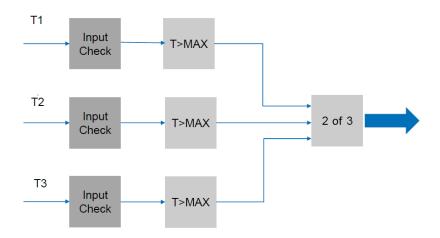

| Abbildung 3: Funktionsrelevante 2-von-3 Temperatur-Auswahlschaltung30                                                     |

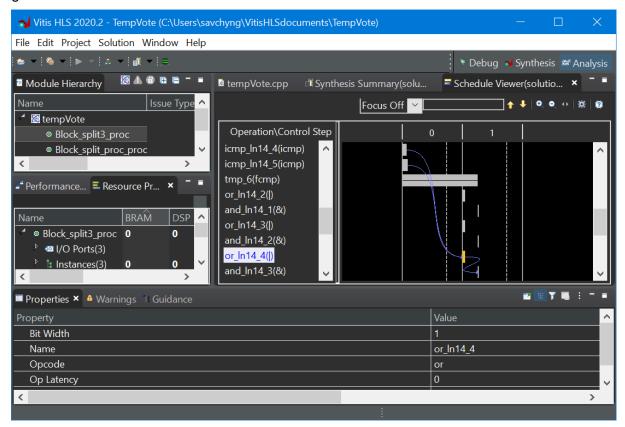

| Abbildung 4: Schedule Viewer in Vitis HLS33                                                                               |

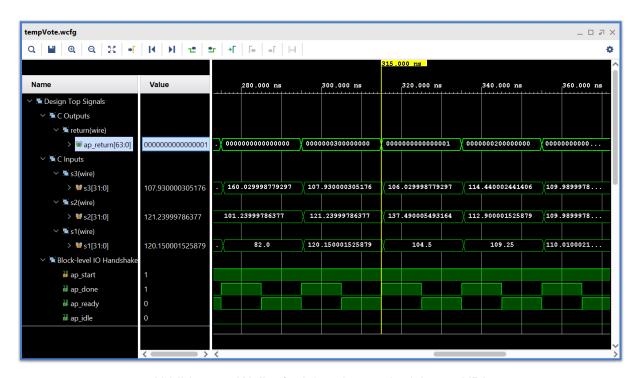

| Abbildung 5: Wellenfunktion der synthetisierten HDL34                                                                     |

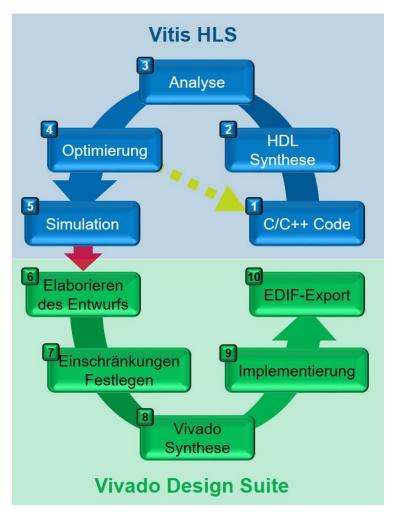

| Abbildung 6: Entwicklungsschritte in Vitis HLS und Vivado35                                                               |

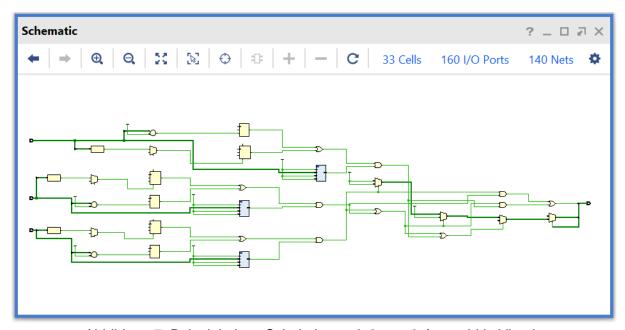

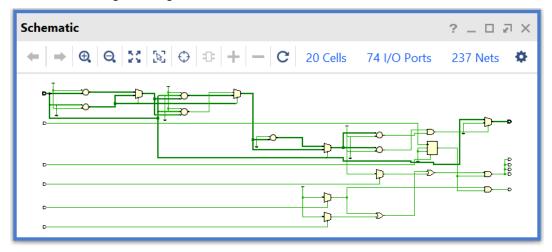

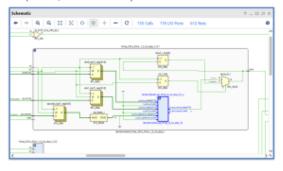

| Abbildung 7: Beispiel eines Schaltplans mit 2-von-3-Auswahl in Vivado36                                                   |

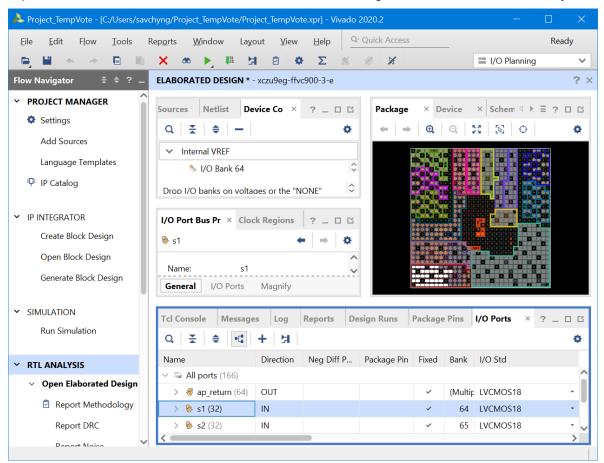

| Abbildung 8: Zuweisung von Eingabe-/Ausgabe-Ports auf Pins in des Ziel-FPGA37                                             |

| Abbildung 9: C++ Codeabschnitt der Eingangsprüfung (Vitis HLS 2021.1)39                                                   |

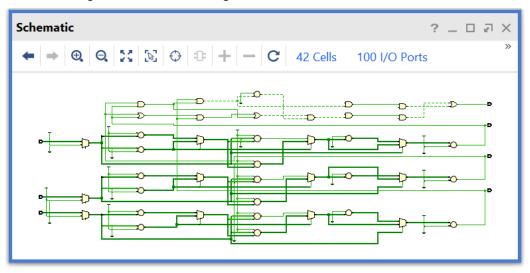

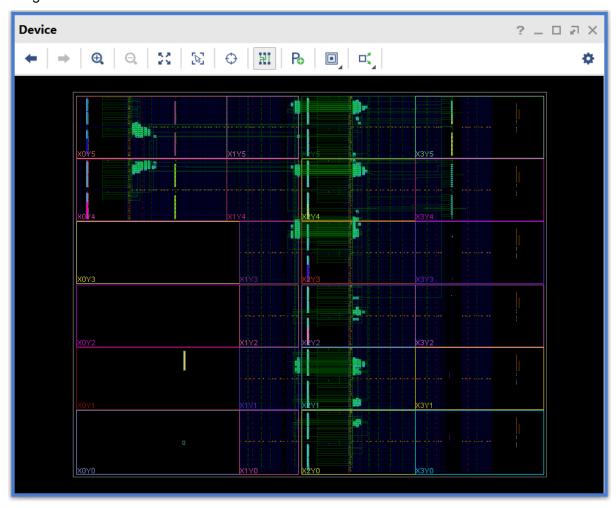

| Abbildung 10: Schaltplan des FPGA-Designs zur Eingangsprüfung (Vivado 2021.1)40                                           |

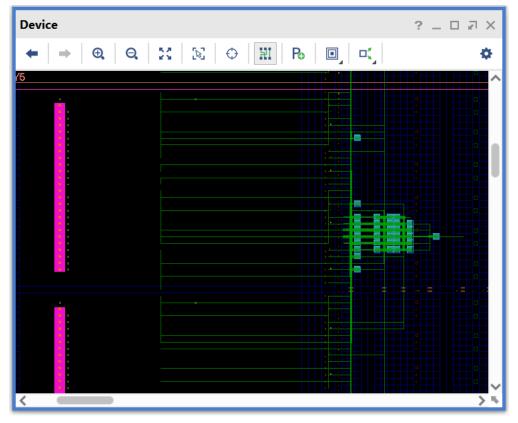

| Abbildung 11: FPGA-Architektur der Eingangsprüfung (Vivado 2021.1)40                                                      |

| Abbildung 12: C++ Codeabschnitt der 2-von-3-Auswahlschaltung (Vitis HLS 2021.1)41                                         |

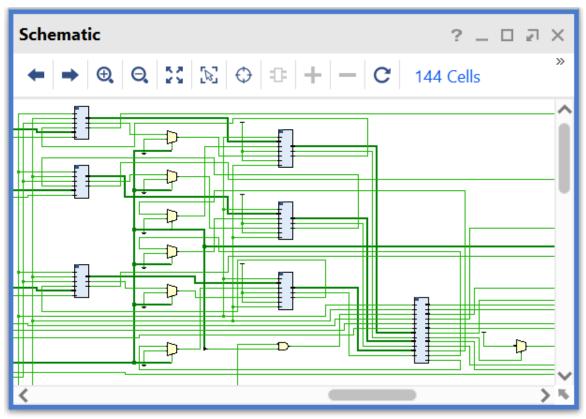

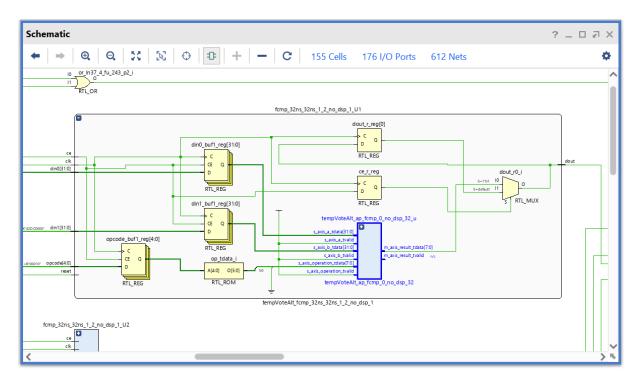

| Abbildung 13: Schaltplan der 2-von-3-Auswahlschaltung (Vivado 2021.1)42                                                   |

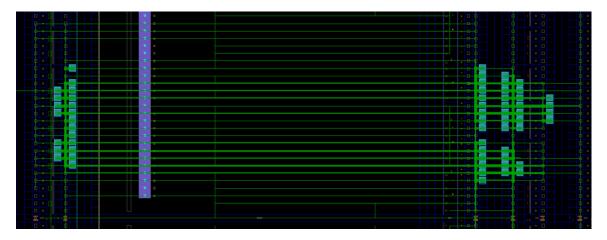

| Abbildung 14: Vereinfachter Schaltplan der 2-von-3-Auswahlschaltung (Vivado 2021.1)42                                     |

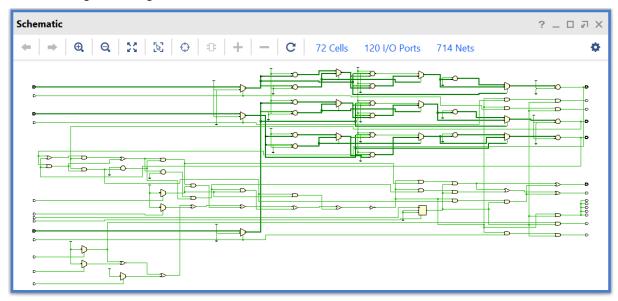

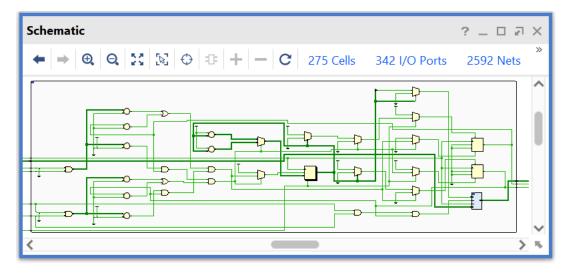

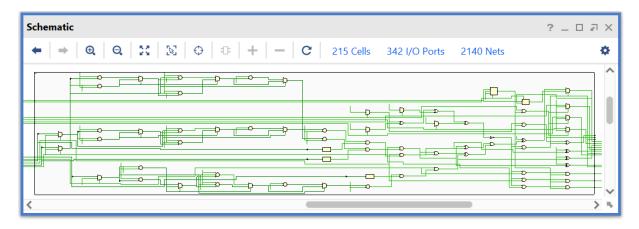

| Abbildung 15: Schaltplanabschnitt der Redundanzschaltung (Vivado 2021.1)43                                                |

| Abbildung 16: Eingangsprüfung der Redundanzschaltung (Vivado 2021.1)44                                                    |

| Abbildung 17: 2-von-3-Auswahlelement der Redundanzschaltung (Vivado 2021.1)44                                             |

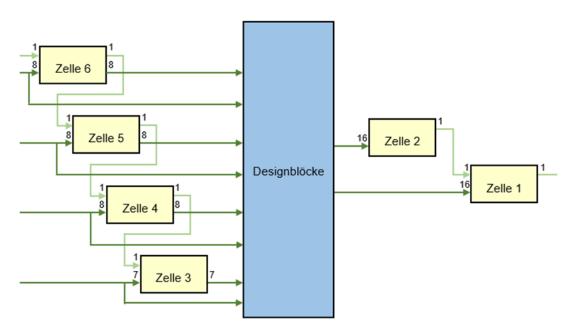

| Abbildung 18: FPGA-Architektur der Redundanzschaltung (Vivado 2021.1)45                                                   |

| Abbildung 19: Ausschnitt der FPGA-Architektur der Redundanzschaltung (Vivado 2021.1) .45                                  |

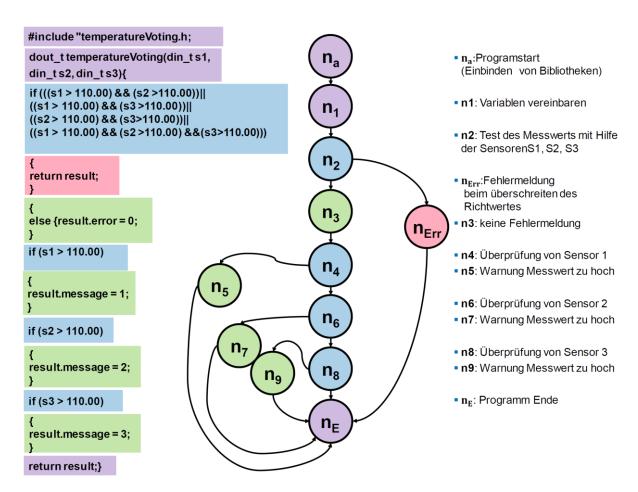

| Abbildung 20: Kontrollflussgraph des Programms der Auswahlschaltung48                                                     |

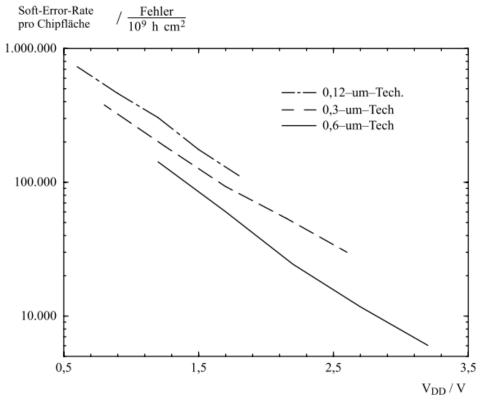

| Abbildung 21: Soft-Error-Rate pro Chipfläche für das Gehäuse als Alphapartikelquelle (typische Technologieparameter) [48] |

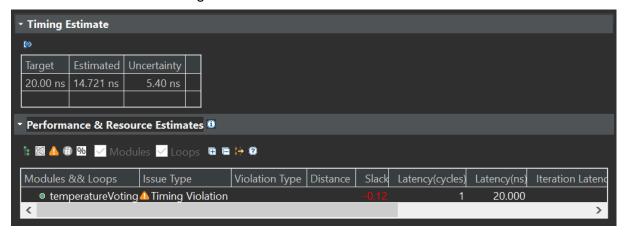

| Abbildung 22: Zeitlicher Verstoß im Synthesebericht der 2-von-3-Auswahlschaltung57                                        |

| Abbildung 23: Untermodul mit Vivado-IP im Schaltplan der 2-von-3-Auswahlschaltung60                                       |

| Abbildung 24: Untersuchte Zellen der Komplexitätsanalyse                                                                  |

# **VERZEICHNIS DER TABELLEN**

| Tabelle 1:  | Technologien programmierbarer logischer Schaltungen               | 4  |

|-------------|-------------------------------------------------------------------|----|

| Tabelle 3:  | Entwicklungswerkzeuge zur Erstellung von FPGA-Designs             | 17 |

| Tabelle 4:  | Hersteller und Typen von FPGAs                                    | 19 |

| Tabelle 5:  | Komponenten des Komplexitätsvektors für FPGA-basierte Anwendungen | 24 |

| Tabelle 6:  | Beispiel des MC/DC Test                                           | 49 |

| Tabelle 7:  | Potenzielle Fehlerquellen bei der FPGA-Entwicklung                | 62 |

| Tabelle 8:  | Fehlerinjektion von postulierten FPGA-Fehlermodi                  | 69 |

| Tabelle 9:  | Komplexitätsvektoren der FPGA-Designs                             | 71 |

| Tabelle 10: | Komplexitätsvektoren von Designvarianten der Auswahlschaltung     | 75 |

| Tabelle 11: | Komplexitätsvektoren von Designvarianten der Eingangsprüfung      | 77 |

# **REVISIONSBLATT**

| Datum      | Rev. | Änderungen                                                                                                                                                                                                   | Bearbeiter                   |

|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 23.02.2023 | 1    | Entwurf                                                                                                                                                                                                      | Heigl<br>Savchyn<br>Woelbing |

| 04.05.2023 | 1.1  | Aktualisierung: Komplexitätsbasiertes Testen                                                                                                                                                                 | Heigl<br>Savchyn             |

| 25.07.2023 | 2    | Einarbeitung aller Kommentare von JDE. Kapitel zu Komplexitätsanalyse eingefügt. Kapitel zu Qualifizierungskriterien eingefügt. Zusammenfassung aktualisiert. Publikation und Präsentationsfolien eingefügt. | Heigl                        |

| 24.10.2023 | 3    | Überarbeitung nach internem Review                                                                                                                                                                           | Miedl<br>Heigl               |

| 17.11.2023 | 4    | Überarbeitung gemäß Kommentaren der<br>Auftraggeberin                                                                                                                                                        | Miedl<br>Heigl<br>Woelbing   |

| 28.11.2023 | 5    | Redaktionelle Korrekturen                                                                                                                                                                                    | Heigl                        |

#### **KURZFASSUNG**

Der Einsatz digitaler Leittechnik in Kernkraftwerken (KKW) führte zu einer zunehmenden Diskussion darüber, wie Methoden für eine Bewertung der Zuverlässigkeit solcher Systeme geschaffen werden können. Die Probleme ergeben sich zum einen aus dem Mangel an allgemein akzeptierten Modellen zur quantitativen Bewertung von Verfügbarkeit und Zuverlässigkeit, und zum anderen aus der Problematik der Integration solcher Modelle in die Bewertung der Zuverlässigkeit eines Gesamtsystems. Dennoch werden immer komplexere Systeme implementiert, um den wachsenden Anforderungen an die Funktionalität gerecht zu werden. Daher wurde die Frage nach einer Methode zur Bewertung der Zuverlässigkeit von Systemen, die auf Software oder programmierbarer Logik basieren, immer dringlicher.

Für die sicherheitsrelevante Leittechnik von KKW sind zunehmend Geräte auf der Basis programmierbarer logischer Schaltungen wie Field Programmable Gate Array (FPGA) auf dem Markt verfügbar. Dementsprechend besteht die Notwendigkeit, Methoden zur Bewertung ihrer Sicherheit und Zuverlässigkeit zu ermitteln oder zu entwickeln. Es ist zu erwarten, dass programmierbare logische Schaltungen zunehmend während der Restlebensdauer von KKWs und darüber hinaus in Nach- und Umrüstungsmaßnahmen sowie zur Deckung des Ersatzbedarfs (Redesign von Komponenten) eingesetzt werden.

In vorangegangenen Forschungsvorhaben (FKZ-3614R01310 [9]) wurde ein Ansatz zur Bestimmung der Komplexität auf Basis eines Komplexitätsvektors entwickelt, und die zugrundeliegende Methode auf programmierbare logische Schaltungen erweitert. Der Komplexitätsvektor definiert eine Metrik, welche die spezifischen Eigenschaften und Merkmale der programmierbaren Logik digitaler Leittechniksysteme widerspiegelt. Das Komplexitätsmessverfahren und seine praktische Anwendbarkeit wurden durch Untersuchung und Anwendung auf mehrere beispielhafte Geräte demonstriert, wie sie in kerntechnischen Leittechnikanwendungen eingesetzt werden.

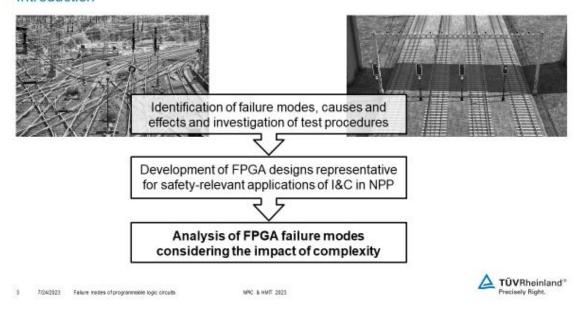

In dem vorliegenden Bericht werden Fehlermodi von FPGA-basierten Leittechnik-Komponenten identifiziert. Ferner werden Fehlerursachen und Auswirkungen sowie verschiedene Testverfahren zur Sicherheits- und Zuverlässigkeitsbewertung analysiert. Ziel ist es, zu untersuchen, welche Fehlermodi die Testverfahren zu erkennen vermögen. Die Tests werden an eigens im Rahmen des Forschungsvorhabens entwickelten FPGA-Designs durchgeführt, die repräsentativ für sicherheitsrelevante Anwendungen in der Leittechnik von Kernkraftwerken sind. Die Komplexität der entwickelten FPGA-Designs wurde bei der Generierung der Testfälle besonders berücksichtigt. Der Grundgedanke war, komplexe Abschnitte des Designs intensiv zu testen, um eine optimierte Testabdeckung zu erreichen. Die Testverfahren wurden durch Anwendung von Fehlerinjektionen auf mögliche Schwachstellen untersucht und die erreichte Testabdeckung bewertet.

#### **ABSTRACT**

Utilization of digital I&C for application in nuclear power plants (NPPs) led to a growing discussion on how methods can be developed to assess the reliability of such systems. The issues involved arise, on the one hand, from a lack of commonly accepted models for quantitative evaluation of availability and reliability, and on the other hand from the problem of integrating such models into the assessment of the reliability of an overall system. Nevertheless, increasingly complex systems are being implemented to satisfy growing requirements on functionality. Therefore, the need for a method to evaluate the reliability of systems based on software or on programmable logic became even more urgent.

For safety-related I&C of NPPs, devices based on programmable logic circuits such as Field Programmable Gate Array (FPGA) are increasingly available on the market. Accordingly, there is a need to identify or develop methods for assessing their safety and reliability. It is to be expected that programmable logic circuits will increasingly be used during the remaining service life of NPPs and beyond in retrofitting and refurbishment measures as well as to cover replacement requirements (redesign components).

In previous research projects (FKZ-3614R01310 [9]) an approach for determining complexity based on a complexity vector was developed, and the underlying method was extended to programmable logic devices. The complexity vector defines a metric that reflects the specific properties and features of programmable logic used in digital I&C systems. The complexity measuring procedure and its practical applicability has been demonstrated by investigation and application to several exemplary devices which are actually used in nuclear I&C applications.

Failure modes of FPGA based I&C components are identified in this report. Moreover, their causes and effects as well as various test procedures for safety and reliability assessment are analyzed. The aim is to investigate which failure modes the test procedures are able to detect. The tests are performed on FPGA designs developed specifically as part of the research, which are representative of safety-relevant I&C applications in NPP. The complexity of the developed FPGA designs was particularly taken into account when the test cases were generated. The basic idea was to test complex sections of the design more intensively in order to achieve an optimized test coverage. Test procedures were examined for potential weaknesses using fault injection and the achieved test coverage was assessed.

#### 1 EINLEITUNG

In den folgenden Unterkapiteln wird auf die Beauftragung, Zielsetzung und relevante Technologien des Vorhabens eingegangen.

# 1.1 Beauftragung

Mit Schreiben vom 08.09.2020 beauftragte das Bundesamt für die Sicherheit der nuklearen Entsorgung (BASE) im Auftrag des Bundesministeriums für Umwelt, Naturschutz, nukleare Sicherheit und Verbraucherschutz (BMUV) die TÜV Rheinland Industrie Service GmbH mit der Analyse von Fehlermodi von programmierbaren logischen Schaltungen in der Sicherheitsleittechnik von Kernkraftwerken. Diese Arbeiten sollen auch zur Aktualisierung und Fortschreibung des deutschen und internationalen Normenwerks und des kerntechnischen Regelwerks beitragen. Die im Vorhaben angewandte Methodik zur Komplexitätsmessung von programmierbarer Logik setzt auf den Ergebnissen von Vorläuferprojekten [5] und [9] auf.

#### 1.2 Zielsetzung

In der Sicherheitsleittechnik von Kernkraftwerken kommen zunehmend Geräte auf den Markt, die auf programmierbaren logischen Schaltungen wie FPGA basieren. Entsprechend besteht der Bedarf, Methoden zur Bewertung ihrer Sicherheit und Zuverlässigkeit zu identifizieren bzw. zu entwickeln. Auch in Deutschland ist damit zu rechnen, dass während der Restlaufzeit von KKWs und darüber hinaus bei Nach- und Umrüstmaßnahmen sowie zur Deckung des Ersatzbedarfs (Redesign-Komponenten) zunehmend entsprechende Geräte eingesetzt werden.

Da die Einsatzzeit von FPGA-basierte Leittechnik im Vergleich zu CPU-basierter Leittechnik in KKWs kürzer ist, gibt es eine geringere Datenbasis, um belastbare Aussagen zur Zuverlässigkeit oder dem Fehlerpotential von FPGA-Anwendungen zu treffen. FPGAs stellen grundsätzlich eine neuere Technologie dar, die zudem einen hohen Innovationsgrad aufweist, weshalb weitere Forschung einen wertvollen Beitrag zur Entwicklung und Erprobung von Bewertungsmethoden leisten kann. In diesem Vorhaben werden Fehlermodi FPGA-basierter Leittechnikkomponenten ermittelt, ihre Ursachen und Auswirkungen analysiert, und verschiedene Testverfahren zur Sicherheits- und Zuverlässigkeitsbewertung erprobt. Dabei wird untersucht, welche Fehlermodi die Testverfahren aufzudecken vermögen. Die Testverfahren werden an eigens im Rahmen des Vorhabens entwickelten repräsentativen FPGA-Designs erprobt.

Im Rahmen des vom BMU geförderten Projektes "Komplexität und Fehlerpotential bei softwarebasierter digitaler Sicherheitsleittechnik" [9] wurde eine Methodik zur Ermittlung von Komplexitätsmetriken für softwarebasierte digitale Sicherheitsleittechnik entwickelt und für die Anwendung auf programmierbare logische Schaltungen erweitert. Ziel dieses Forschungsprojekts ist, auf der Grundlage von FPGA-Designs, die eigens mit einem entsprechenden Designwerkzeug erstellt werden, eingehende Analysen durchzuführen. Dabei wird die in früheren Forschungsvorhaben ausgearbeitete Methodik für die Ermittlung der Komplexität auf die verschiedenen FPGA-Designs angewendet. Bei der Generierung der Testfälle wird der Komplexitätsaspekt besonders berücksichtigt. Ziel dabei ist, komplexere Bereiche der FPGA-Designs verstärkt zu testeten, um so eine möglichst optimale Testabdeckung zu erreichen. Die Untersuchung eigens entwickelter Designs ermöglicht es

Dateiname: ISTec-A-4013\_A\_Bericht Rev.5.docx Seite 3 von 105

außerdem, die angewendeten Testverfahren durch Fehlerinjektion auf Schwachstellen hin zu untersuchen und die erreichte Testabdeckung zu bewerten.

Anhand der gewonnenen Erkenntnisse über die Fehlermodi FPGA-basierter Leittechnik und die Leistungsfähigkeit verschiedener Testverfahren werden Kriterien für die Qualifizierung von FPGA-Designs abgeleitet. Ebenso werden bestehende Qualifizierungsanforderungen in verschiedenen Regelwerken vor dem Hintergrund der Ergebnisse kritisch hinterfragt.

#### 1.3 Technologien

Beginnend in den 1970er und 80er Jahren fanden Entwicklungen der Mikroelektronik statt, die für die Leittechnik von Kernkraftwerken von Bedeutung sind. Es wurde eine zunehmende Integration von Funktionalität bei integrierten Schaltkreisen (wie z.B. Mikroprozessoren und programmierbaren logischen Schaltungen) möglich. Die Entwicklung verlief dabei von zentralen Rechenanlagen zur Steuerung und Regelung von Prozessen zu dezentralen Industrie-Computern und Anwendung zur von Mikrocontrollern bzw. Speicherprogrammierbaren Steuerungen. Diese Entwicklung ermöglichte einen zunehmenden Einsatz softwarebasierter Systeme für leittechnische Funktionen.

Außerdem führten die Verbesserungen der Herstellungstechnologien dazu, dass integrierte Schaltkreise, anwendungs- bzw. kundenspezifische Schaltkreise (ASIC) und programmierbare Schaltkreise (PLD) kostengünstig zu produzieren waren. Über FPLAs ab Mitte der 1980er Jahre führte die Entwicklung zu den hochintegrierten CPLDs und FPGAs der heutigen Zeit.

Tabelle 1: Technologien programmierbarer logischer Schaltungen

| Bezeichnung | Beschreibung                                                                                                                                                    |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PLD         | Programmable Logic Device (z.B. PLA, PROMs)                                                                                                                     |  |  |

|             | programmierbare integrierte Schaltkreise                                                                                                                        |  |  |

|             | FPGAs und CPLDs sind spezielle PLDs                                                                                                                             |  |  |

|             | ca. ab 1980 verfügbar                                                                                                                                           |  |  |

| PLA, FPLA   | Programmable Logic Array, Field Programmable Logic Array                                                                                                        |  |  |

|             | integrierte Schaltkreise mit programmierbaren Logik-Feldern, die logische Grundverknüpfungen wie UND/ODER- Gatter, Addierer, Zähler, Flipflops usw. ermöglichen |  |  |

|             | geringer bis mittlerer Integrationsgrad                                                                                                                         |  |  |

|             | ca. ab 1980 verfügbar                                                                                                                                           |  |  |

Dateiname: ISTec-A-4013\_A\_Bericht Rev.5.docx Seite 4 von 105

| Bezeichnung | Beschreibung                                                                                     |  |  |

|-------------|--------------------------------------------------------------------------------------------------|--|--|

| PAL         | Programmable Array Logic, sind spezielle PLAs                                                    |  |  |

|             | integrierte Schaltkreise mit programmierbaren Logik-Feldern (nur UND-<br>Verknüpfungen)          |  |  |

|             | geringer Integrationsgrad                                                                        |  |  |

|             | ca. ab 1980 verfügbar                                                                            |  |  |

| CPLD /      | Complex Programmable Logic Device                                                                |  |  |

| SPLD        | bestehen aus zusammengeschalteten Simple Programmable Logic Devices                              |  |  |

|             | CPLDs sind integrierte Schaltkreise mit:                                                         |  |  |

|             | programmierbarer UND/ODER-Matrix und logischen Funktionen                                        |  |  |

|             | programmierbaren Verknüpfungslogiken und Rückkopplungen mit bestimmbarem Zeitverhalten           |  |  |

|             | programmierbaren Eingabe- und Ausgabeblöcken                                                     |  |  |

|             | mit hohem bis sehr hohem Integrationsgrad (VLSI-Technologie, bis 10.000 Gatter)                  |  |  |

|             | ca. ab Anfang der 1990er Jahre verfügbar                                                         |  |  |

| FPGA        | Field Programmable Gate Array                                                                    |  |  |

|             | integrierte Schaltkreise mit:                                                                    |  |  |

|             | programmierbaren Logik-, Speicher-, Ein- und Ausgabe- und Routingfeldern                         |  |  |

|             | verschieden programmierbarer Verknüpfungslogik mit Einfluss auf das Zeitverhalten der Logikpfade |  |  |

|             | sehr hohem Integrationsgrad (VLSI-Technologie, bis 100.000 Gatter-<br>Äquivalente)               |  |  |

|             | ca. ab erster Hälfte der 1990er Jahre verfügbar                                                  |  |  |

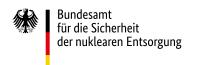

Der Entwicklungsgang der unterschiedlichen Technologien, bis hin zum System on a Chip (SOC), ist in Abbildung 1 dargestellt.

Abbildung 1: Architekturtypen von programmierbarer Logik [1]

In [1] werden FPGAs und CPLDs wie folgt gegenübergestellt: CPLDs haben ihren Ursprung in PALs, die wiederum aus den PLAs hervorgegangen sind, sowie der Generic Array Logic (GAL). Die funktionelle Einheit der CPLD besteht aus Mikrozellen, von denen jede eine kombinatorische UND/ODER-Registerfunktion ausführt. Die funktionelle Logik in einem Block ist eine Matrix logischer Terme. Über ein Term-Verteilungs-Diagramm kann jede Mikrozelle auf eine Teilmenge dieser Terme zugreifen. Umschaltmatrizen ordnen die Signale der Ausgänge der funktionalen Einheit und der Eingabe/Ausgabe-Einheit zu. Im Gegensatz zu FPGAs, bei denen die Verbindungen segmentiert sind (parallele Abarbeitung), weisen CPLDs ein kontinuierliches System von Verbindungen (serielle Abarbeitung) auf. Die FPGA-Architektur hat ihren Ursprung in verbundenen Gate Arrays. Die interne Architektur besteht aus einem Satz konfigurierbarer logischer Einheiten, die regulär angeordnet und mit Leitkanälen verbunden sind. Basisblöcke wie z.B. logische Zellen und Look-Up Tables werden als konfigurierbare Logikblöcke verwendet. Diese Module weisen wiederum eine gegliederte Architektur von internen Verbindungen auf.

#### 2 BEGRIFFE UND ABKÜRZUNGEN

Im Folgenden sind die Begriffe und Abkürzungen definiert, die in diesem Bericht verwendet werden.

#### 2.1 Begriffe

Im Folgenden sind Begriffe definiert, die in diesem Bericht verwendet werden.

#### 2.1.1 Basisblock

Wesentliche Grundstruktur eines FPGA, bestehend aus einer vielfach wiederholten konfigurierbaren logischen Schaltung (z.B. Look-up Tables und Register). Die Struktur der Basisblöcke ist herstellerspezifisch.

Anmerkung: Die leittechnischen Funktionen einer FPGA-Anwendung ergeben sich aus der Verschaltung der Basisblöcke, die aus einer Hierarche von Bibliotheken in der Netzliste des FPGAs hervorgehen.

#### 2.1.2 BIST

Ein "Built-In-Self-Test" (BIST) beschreibt die eingebaute Eigendiagnose eines programmierbaren logischen Schaltkreises. Dabei verfügen ausgewählte elektronische Bausteine über eine integrierte Testschaltung, welche Testsignale erzeugt, die in der Regel mit vorgegebenen richtigen Antwort-Signalen verglichen werden.

#### 2.1.3 CPLD und FPGA

Programmierbare logische Schaltungen, die in der Sicherheitsleittechnik von Kernkraftwerken zum Einsatz kommen, beruhen maßgeblich auf Technologien wie programmierbaren logischen Bausteinen (Programmable Logic Device, PLD), feldprogrammierbare logische Gatter (Field Programmable Gate Array, FPGA) und komplexen programmierbaren logischen Bausteinen (Complex Programmable Logic Device, CPLD).

Während bei herkömmlichen anwendungsspezifischen integrierten Schaltkreisen (ASIC) die Funktionen in der Regel bereits festgelegt sind, können die internen Ressourcen (z.B. programmierbare Basisblöcke) des FPGA vom Anwender im Rahmen des Entwicklungsprozesses so konfiguriert werden, dass die gewünschte Systemfunktion ausgeführt werden kann. Die programmierbaren Basisblöcke ermöglichen logische Grundverknüpfungen wie UND/ODER-Gatter, Addierer, Zähler, Flipflops usw. Die hierbei verwendeten Basisblöcke weisen eine gegliederte Architektur von internen Verbindungen auf.

#### 2.1.4 Einschränkungen (engl.: constraints)

Vorgaben, die bei der Entwicklung eingehalten werden müssen, damit der Entwurf erforderliche Eigenschaften aufweist.

#### 2.1.5 Fehlermodi

Art des Auftretens eines Ausfalls.

(online IEC vocabulary: "manner in which failure occurs").

#### 2.1.6 Funktionsbaustein

Repräsentation eines Elements mit begrenzter Funktionalität in einer graphisch orientierten Programmiersprache.

Dateiname: ISTec-A-4013\_A\_Bericht Rev.5.docx Seite 7 von 105

Anmerkung: Mit Hilfe eines Funktionsbausteins können neben Elementarfunktionen durch deren Verschaltung nahezu beliebige Funktionen implementiert werden, womit sich leittechnische Funktionen realisieren lassen. Aus der Verschaltung von Funktionsbausteinen, dem Funktionsplan, ergeben sich die leittechnischen Funktionen einer speicherprogrammierbaren Steuerung.

#### 2.1.7 FPGA-Anwendung

Konfiguration eines FPGA zur Umsetzung einer gewünschten Funktion. Die Entwicklung des FPGA-Programms basiert auf dem FPGA-Design.

#### 2.1.8 FPGA-Design

Softwarebasierter Entwurf einer FPGA-Anwendung.

Anmerkung: In diesem Vorhaben wird der Entwurf basierend auf einer Spezifikation in C/C++ Code entwickelt und mittels Synthese in HDL erzeugt. Nach weiteren Simulationen, Optimierungen und Synthesen wird eine Electronic Design Interchange Format (EDIF) Netzliste des Entwurfs generiert. Der Begriff FPGA-Design beschreibt den softwarebasierten Entwurf dabei unabhängig von dem jeweiligen Entwicklungsschritt bzw. der verwendeten Sprache.

#### 2.1.9 Hardware-Beschreibungssprache (HDL)

Sprache, die dazu verwendet wird, die Funktionen und/oder die Struktur einer elektronischen Komponente für Dokumentation, Simulation oder Synthese formal zu beschreiben [4].

Anmerkung: Die verbreitetsten HDLs sind VHDL (IEEE 1076) und Verilog (IEEE 1364).

#### 2.1.10 HDL-programmierter Baustein (HPD)

Integrierter Schaltkreis, der (für leittechnische Systeme in Kernkraftwerken) unter Verwendung von Hardware-Beschreibungssprachen und zugehörigen Softwarewerkzeugen konfiguriert wird [4].

Anmerkung 1: HDLs und zugehörige Werkzeuge (z. B. Simulatoren, Synthesewerkzeuge) werden verwendet, um die Anforderungen in eine geeignete Konfiguration von vorentwickelten mikroelektronischen Ressourcen umzusetzen.

Anmerkung 2: Bei der Entwicklung von HPDs können vorentwickelte Blöcke verwendet werden.

Anmerkung 3: HPDs basieren typischerweise auf FPGAs, PLDs oder ähnlichen mikroelektronischen Technologien.

#### 2.1.11 Komplexität

Die Definition eines allgemeinen Begriffs "Komplexität" ist ein außerordentlich schwieriges Unterfangen. Deshalb wird dieser Begriff in unterschiedlichen Gebieten unterschiedlich definiert. Zusätzlich ist er vom Wissen, das ein Betrachter in einem speziellen Gebiet besitzt, bestimmt. Deshalb wird in diesem Bericht der Begriff "Komplexität" als Kombination messbarer Größen angesehen. Sowohl die einzelnen Messgrößen als auch deren Kombination werden als Komplexitätsmaß (bzw. synonym als Komplexitätsmetrik) bezeichnet.

#### 2.1.12 Komplexitätsbewertung

Der Prozess der Beurteilung einer Komplexitätsmessung.

Dateiname: ISTec-A-4013\_A\_Bericht Rev.5.docx Seite 8 von 105

#### 2.1.13 Komplexitätsmetrik, Komplexitätsmaß

Eine Komplexitätsmetrik ist eine Funktion, die eine Software-Einheit in Bezug auf die Qualitätseigenschaft "Komplexität" auf einen Zahlenwert abbildet.

Anmerkung 1: Wichtige Komplexitätsmetriken sind das McCabe-Maß (zyklomatische Komplexität), die Knotenmetrik und das Verknüpfungsmaß [5].

Anmerkung 2: Die zyklomatische Komplexität und die Knotenmetrik sind Kontrollflussmaße. Das Verknüpfungsmaß nach [5] ist ein Datenflussmaß.

#### 2.1.14 Komplexitätswert, Komplexitätsvektor und Komplexitätsmessung

Der Komplexitätswert stellt eine messbare oder berechenbare Maßzahl dar.

Die Zusammenfassung von Komplexitätswerten erfolgt z.B. in einem Komplexitätsvektor.

Unter Komplexitätsmessung wird der Prozess der Bestimmung der Werte des Komplexitätsvektors für ein bestimmtes Objekt einer Objektklasse zusammengefasst.

#### 2.1.15 Programmierbarer logische Baustein (engl.: programmable logic device PLD)

Integrierter Schaltkreis, der aus logischen Elementen mit einer Verbindungsstruktur besteht, von denen ein Teil vom Anwender programmierbar ist [4].

Anmerkung: Programmierbarer logischer Baustein wird in diesem Bericht als programmierbare logische Schaltung bezeichnet.

#### 2.1.16 Zustandsmaschine (engl.: finite state machine)

Eine Zustandsmaschine ist gemäß [21] das abstrakte Modell eines Automaten mit einfach strukturiertem Speichervermögen. Das Verhalten dieser Zustandsmaschine ist dadurch gekennzeichnet, dass für eine begrenzte Anzahl von Eingangssignalkombinationen (Eingangszuständen) ausgangsseitig jeweils definierte Ausgangszustände angenommen werden. Das Verhalten einer Zustandsmaschine kann in einem Diagramm dargestellt werden. Hierbei wird für jeweils einen Eingangsstatus ein Ausgangsstatus erzeugt.

#### 2.1.17 Testbank (Simulation)

Eine Simulation, die erstellt wird, um die Funktionalität des FPGAs zu überprüfen. Bei der Erstellung der Testbank wird ein funktionaler Zusammenhang zum prüfenden FPGA hergestellt.

Anmerkung: Die Testbank wird in VHDL oder Verilog geschrieben, ist jedoch selbst nicht zwingend synthesefähig.

#### 2.1.18 Wellenfunktion

Die Wellenfunktion stellt den zeitlichen Verlauf der angesteuerten Funktion für den Bereich der Ein- und Ausgangssignale eines FPGA dar. Wellenfunktionen werden auf Grundlage diskreter Signale, mit den Werten 0 und 1, dargestellt. Ein Wert von 1 bedeutet, dass die jeweilige Funktion zum Zeitpunkt  $t_1$  angesteuert und über das Zeitintervall  $t_{d1}$  ausgeführt wird. Ein Wert von 0 bedeutet, dass die Funktion zum Zeitpunkt  $t_2$  und über das Zeitintervall  $t_{d2}$  nicht angesteuert wird.

Dateiname: ISTec-A-4013\_A\_Bericht Rev.5.docx Seite 9 von 105

#### 2.1.19 Platzieren

Das Platzieren (engl.: "place-and-route") ist der Prozess der Abbildung des erstellten FPGA-Designs auf den FPGA-Baustein sowie das logische Verbinden der elektronischen Komponenten zur Realisierung der FPGA-Funktionen.

# 2.1.20 Synthese

Die Synthese ist ein Prozess, bei dem basierend auf vorgegebenen Eigenschaften ein Programm, beispielsweise eine Netzliste für ein FPGA, erzeugt wird. Die Eigenschaften sind dabei durch Modelle, Code oder Einschränkungen vorgegeben.

Anmerkung: Im Rahmen des Vorhabens wird bei der Synthese C/C++ Code als Quelle verwendet und in HDL Code umgewandelt, dessen funktionales Verhalten äquivalent zum C/C++ Code sein soll.

Dateiname: ISTec-A-4013\_A\_Bericht Rev.5.docx Seite 10 von 105

# 2.2 Abkürzungen

Im Folgenden sind die Abkürzungen definiert, die in diesem Bericht verwendet werden.

| ASIC                                  | Application-Specific Integrated Circuit          |  |  |

|---------------------------------------|--------------------------------------------------|--|--|

| BIST                                  | Built-In-Self-Test                               |  |  |

| CPU                                   | Central Processing Unit                          |  |  |

| CPLD                                  | Complex Programmable Logic Device                |  |  |

| EDIF                                  | Electronic Data Interchange Format               |  |  |

| EN                                    | Europäische Norm                                 |  |  |

| EU                                    | Europäische Union                                |  |  |

| FB                                    | Funktionsblock                                   |  |  |

| FP                                    | Funktionsplan                                    |  |  |

| FPGA                                  | Field Programmable Gate Array                    |  |  |

| FMEA                                  | Failure Mode and Effect Analysis                 |  |  |

| FPLA                                  | Field Programmable Logic Array                   |  |  |

| HDL                                   | Hardware Description Language                    |  |  |

| HPD                                   | (HDL) Programmed Device                          |  |  |

| HW                                    | Hardware                                         |  |  |

| I&C                                   | Instrumentation and Control                      |  |  |

| IAEA                                  | International Atomic Energy Agency               |  |  |

| IEC                                   | International Electrotechnical Commission        |  |  |

| IEEE                                  | Institute of Electrical and Electronic Engineers |  |  |

| ISO                                   | International Organization for Standardization   |  |  |

| ISTec                                 | Institut für Sicherheitstechnologie              |  |  |

| IDE                                   | Integrated Development Environment               |  |  |

| KKW                                   | Kernkraftwerk                                    |  |  |

| LOC                                   | Lines of Code                                    |  |  |

| PAL                                   | Programmable Array Logic                         |  |  |

| · · · · · · · · · · · · · · · · · · · |                                                  |  |  |

| PLA  | Programmable Logic Array         |  |

|------|----------------------------------|--|

| PLD  | Programmable Logic Device        |  |

| PROM | Programmable Read-Only Memory    |  |

| SOC  | System on a Chip                 |  |

| SPLD | Simple Programmable Logic Device |  |

| SSG  | Specific Safety Guide            |  |

| SW   | Software                         |  |

| TR   | TÜV Rheinland                    |  |

| V&V  | Verification and Validation      |  |

# 3 STAND VON WISSENSCHAFT UND TECHNIK ZUM FEHLERPOTENTIAL UND ZU FEHLERMODI BEI FPGA-DESIGNS

Der Teilbericht [8] (siehe Anhang A) fasst unter anderem den Stand von Wissenschaft und Technik zur Analyse der Fehlermodi von programmierbaren logischen Schaltungen in der Sicherheitsleittechnik von Kernkraftwerken zusammen. Dazu wurden Methode Arbeitsergebnisse bezüglich einer zur Messung der Komplexität Anwendungssoftware leittechnischer Automatisierungssysteme herangezogen. Die Ergebnisse Vorläuferprojekts zeigen, dass die erarbeitete Methode der Komplexitätsmessung zusammen mit dem entwickelten Instrumentarium der Analyse-Werkzeuge auf verschiedene programmierbare logische Schaltungen in der Sicherheitsleittechnik von Kernkraftwerken anwendbar ist [9].

Zu den Fehlermodi digitaler Leittechnik im Allgemeinen, aber auch zu programmierbarer Logik wie FPGAs, sowie den Ursachen der Fehlermodi, den Auswirkungen und Möglichkeiten zur Behandlung, gibt es bereits eine Vielzahl an Literatur. Allerding beschäftigen sich die Studien mehrheitlich mit hardwarebasierten Fehlermodi. Dies ist insofern nicht verwunderlich, als dass der FPGA-Chip selbst keine Software oder ein Betriebssystem beinhaltet [19]. Es wurde im Rahmen der Literaturrecherche deutlich, dass auch softwarebasierte Fehlermodi betrachtet werden müssen. Insbesondere durch den vermehrten Einsatz vorgefertigter Software und der immer stärker vertretenen werkzeuggestützten Umsetzung von FPGA-Designs, rücken softwarebasierte Fehlermodi in den Vordergrund. Es zeigte sich, dass die Ursachen softwarebasierter Fehlermodi hierbei im Entwicklungsprozess und vor allem beim Entwurf des FPGA-Designs [2], [15] liegen.

Für das Testen von FPGA-Designs spielen neben den normativ geforderten Verifizierungsund Validierungsverfahren auch die verwendeten Entwicklungswerkzeuge eine große Rolle.

Es handelt sich hierbei in der Regel um Werkzeug-Sets, die außer dem reinen Entwurf des

FPGA-Designs noch weitere Testwerkzeuge anbieten. Sofern innerhalb eines Werkzeug-Sets

sowohl der Entwurf als auch gewisse Tests des FPGA-Designs erfolgen, muss neben der

Korrektheit des Testwerkzeugs ggf. auch die Unabhängigkeit der Testmethode vom

verwendeten Entwicklungswerkzeug nachgewiesen werden. Obwohl Werkzeug-Sets einige

Verifizierungsschritte unterstützen können, ist es nicht ausreichend die V&V-Ergebnisse allein

von diesen Werkzeugen abzuleiten. Es bedarf in jedem Fall einer unabhängigen Verifizierung

und Validierung. Die Korrektheit der implementierten Funktionalität einer FPGA-Anwendung

lässt sich mittels Funktionstests und statischen Analysen nicht vollständig nachweisen [18],

[19]. Im Vergleich zu CPU-basierten Lösungen sind andere Teststrategien erforderlich, die das

zeitliche Verhalten bzw. die Dynamik der Logik analysieren.

Der in Kapitel 4.1 ermittelte Sachstand von Wissenschaft und Technik zu programmierbaren logischen Schaltungen dient als Grundlage für die Auswahl geeigneter Entwicklungswerkzeuge zur Erstellung von FPGA-Designs für die Untersuchungen innerhalb des Vorhabens.

Dateiname: ISTec-A-4013\_A\_Bericht Rev.5.docx Seite 13 von 105

#### 3.1 Fehlermodi bei integrierter digitaler Leittechnik

FPGAs sind eine Form programmierbarer digitaler Hardwarebausteine, die für die Ausführung digitaler Logikfunktionen konfiguriert werden können. Die Programmierung wird mit einer HDL durchgeführt, d.h. FPGAs sind eine Form von HPD. In der Leittechnik von KKW werden FPGAs u.a. im Rahmen von Nachrüstmaßnahmen und zum Ersatz veralteter Systeme eingesetzt.

Fehlermodi lassen sich durch eine Vielzahl von Merkmalen klassifizieren. Sie werden in der Literatur zumeist in drei große Gruppen unterteilt:

- Entwicklungs- oder Entwurfsfehler,

- physikalische Fehler,

- Interaktionsfehler.

Die erste Gruppe ist typisch für Software. Entsprechende Ausfälle treten unter bestimmten Bedingungen (z.B. Eingabedaten) auf. Die zweite Gruppe betrifft zumeist Hardware und wird durch natürliche Ursachen (wie Alterung) verursacht. Die dritte Gruppe ist eine Folge externer Effekte (wie nicht autorisierte Handlungen und Bedienfehler) [2], [3] und [15].

Abgebildet auf den Lebenszyklus digitaler Leittechnik lassen sich die Fehlermodi von FPGAs auf Grundlage deren Ursache in den beiden Bereichen Entwicklung und Betrieb aufteilen [15].

Innerhalb dieses Forschungsvorhabens liegt der Fokus auf softwarebasierten Fehlermodi, daher wird im Weiteren nicht genauer auf physikalische Fehler, deren Ursache in der Hardware (z.B. im Herstellungsprozess) liegt, eingegangen. Die Ursachen der Fehlermodi während des Betriebs umfassen ebenfalls zum Großteil Hardwarefehler, wie z.B. durch Strahlung, Umgebungseinflüsse und Alterungsprozesse. Die Fehlermodi, deren Ursache im Bereich Betrieb auch innerhalb der Software liegt, beziehen sich auf Wartung (bzw. Modifikation) und Cybersecurity.

Die Fehlermodi, deren Ursache im Bereich Entwicklung liegt, sind hingegen mehrheitlich auf fehlerhafte Software zurückzuführen. Hierzu gehören vor allem Fehlermodi mit Bezug auf:

- Zeitliche Aspekte (Signallaufzeiten)

- Logische Fehler (HDL)

- Zustandsautomat (engl.: state machine)

- Eingangssignale und Datentypen

- Soft Processor (d.h. ein vollständig mittels Logiksynthese implementierter Mikroprozessor)

- Vorgefertigte Software

- Wartbarkeit der Software

- Cybersecurity (im Entwicklungsprozess)

Cybersecurity umfasst bei digitaler Leittechnik neben dem Entwurf (Design) auch die Phasen Systemintegration (Engineering) und Betrieb (Operation) [16]. Da für digitale Leittechnik gemäß IEC 62645 Ed. 2 [17] bezüglich der Cybersecurity vor allem böswillige Handlungen berücksichtigt werden, wird auf Fehlermodi, deren Ursachen im Bezug zur Cybersecurity stehen, im Weiteren nicht näher eingegangen.

Dateiname: ISTec-A-4013\_A\_Bericht Rev.5.docx Seite 14 von 105

Es wird deutlich, dass mit Ausnahme von Modifikation und Cybersecurity die Ursache aller softwarebasierten Fehlermodi im Entwicklungsprozess liegt. Dies ist insbesondere deshalb bemerkenswert, da der FPGA-Chip selbst keine Software oder ein Betriebssystem beinhaltet [19]. Die Ursachen softwarebasierter Fehlermodi liegen daher bei der Konfiguration der FPGA-Logik mittels HDL-Code. Die Fehlermodi von FPGAs aus dem Bereich Entwicklung lassen sich anhand ihrer Ursache innerhalb des Entwicklungslebenszyklus aufteilen [15]. Das Auftreten bestimmter Fehler kann an bestimmte Phasen im Lebenszyklus von Leittechnik gebunden sein. Die Ursachen dieser Fehler können dabei bereits in früheren Lebenszyklus-Phasen begründet sein.

Im Umgang mit Fehlermodi bei FPGA-basierter Leittechnik können verschiedene Strategien angewendet werden [18].

- Fehlervermeidung: Durch geeignete Qualitätssicherungsmaßnahmen soll das Auftreten von Fehlern verhindert werden.

- Fehlerbeherrschung: Durch geeignete administrative und technische Maßnahmen (spezielle Handlungsanweisungen im Fehlerfall, Maßnahmen zur Erreichung eines sicheren Zustands) sollen die Auswirkungen von auftretenden Fehlern begrenzt werden.

- Fehlertoleranz: Durch geeignete technische Maßnahmen (z.B. Redundanz, Diversität) sollen negative Auswirkungen auftretender Fehler eingedämmt und die Funktion betroffener Systeme gewährleistet werden.

Eine Besonderheit von FPGA-basierter Logik ist das vergleichsweise komplexe Zeitverhalten. Daher sind statische Analysen und Prüfmethoden für die meisten FPGA-Anwendungen nicht geeignet, um das dynamische Verhalten abzubilden und die Korrektheit des FPGA-Designs zu verifizieren [19]. Für die Behandlung von FPGA-Fehlermodi sind daher Testmethoden, die das zeitliche Verhalten bzw. die dynamischen Eigenschaften der Logik analysieren, erforderlich. Die entsprechenden Testmethoden sind in Kapitel 3.3 zusammengefasst.

Dateiname: ISTec-A-4013\_A\_Bericht Rev.5.docx Seite 15 von 105

# 3.2 Fehlermodi im Zusammenhang mit modellbasierten FPGA-Entwicklungswerkzeugen

In der Regel kommen bei der Erstellung von FPGA-Designs Entwicklungswerkzeuge (Hardware Design Tools) zum Einsatz. Die Entwicklungswerkzeuge für FPGA-Designs sind dabei häufig Bestandteil eines Werkzeug-Sets, das zusätzlich zu dem eigentlichen Entwurf des FPGA-Designs noch Validierungs- und Testwerkzeuge beinhaltet. Diese sollen die Robustheit bzw. Fehlertoleranz der FPGA-Anwendungen und damit die Zuverlässigkeit der Leittechniksysteme erhöhen [18]. Die folgende Betrachtung fokussiert sich hierbei auf modelbasierte ("model-based design") Entwicklungswerkzeuge. Bei diesen modelbasierten Werkzeugen bilden virtuelle Modelle den Mittelpunkt Ihres Entwicklungsprozesses und sollen somit die Art und Weise, komplexe Anwendungen erfolgreich umzusetzen verbessern und die Entwicklungsdauer verkürzen. Bei der Betrachtung von modellbasierten Entwicklungswerkzeugen für das Erstellen von FPGA-Designs sind mehrere Faktoren bei der Bewertung und Auswahl dieser Werkzeuge zu berücksichtigen:

- Lesbarkeit, Länge und Qualität des generierten Codes

- Bedienungsfreundlichkeit und Lernkurve. Dank der höheren Abstraktionsebene, die in der modellbasierten Hardware-Entwurf-Methodik durch die Werkzeuge verwendet wird, ist es möglich, komplexe Algorithmen viel schneller zu erstellen, zu testen und zu implementieren.

- Verfügbarkeit vorhandener Hardware-Bibliotheken.

- Nachvollziehbarkeit (Übersetzung der angewendeten Programmiersprache zur HDL-Beschreibung).

- Kontrollierbarkeit und Rückverfolgbarkeit der generierten Anwendung.

- Feinabstimmung des generierten Codes auf modellbasierter Abstraktionsebene z.B. zur Beschleunigung der Methodik.

Die durchgeführten Recherchen ergaben, dass bereits mehrere modellbasierte Entwicklungswerkzeuge für FPGA-Designs auf dem Markt sind. Die folgende Tabelle gibt einen Überblick zu gängigen Entwicklungswerkzeugen. Für jedes Werkzeug ist zudem die jeweils verwendete Sprache für den generierten Code aufgeführt. Obwohl die meisten Werkzeuge HDL-Code erzeugen, kann sich die Codeausgabe erheblich unterscheiden.

Dateiname: ISTec-A-4013\_A\_Bericht Rev.5.docx Seite 16 von 105

Tabelle 3: Entwicklungswerkzeuge zur Erstellung von FPGA-Designs

| Hersteller         | Produkt                 | Sprache     |

|--------------------|-------------------------|-------------|

| Mathurada          | Simulink HDL Coder      | HDL         |

| Mathworks          | Real-Time Workshop      | ANSI C, C++ |

| Viliny             | System Generator        | HDL         |

| Xilinx             | Accel DSP               | HDL         |

| Silicon Software   | VisualApplets           | HDL         |

| Synplicity         | Synplify DSP            | HDL         |

| Altoro             | DSP Builder             | HDL         |

| Altera             | SOPC Builder            | HDL         |

| Universität Leiden | Compaan/Laura           | HDL         |

| Bluespec           | Bluespec System Verilog | Verilog     |

| Synfora            | Pico Express            | RTL/SystemC |

| A cility           | Agility MCS             | С           |

| Agility            | DK Design Suite         | HDL         |

| Scilab             | Scicos-HDL              | HDL         |

Die Fehlermodi der Entwicklungswerkzeuge zur Erstellung von FPGA-Designs entsprechen im Allgemeinen den Fehlermodi von Software-Entwicklungswerkzeugen. Dazu gehören:

- Fehlerhafte Editoren zur Generierung der FPGA-Netzlisten.

- Fehlerhafte Umsetzung des erzeugten logischen Funktionsplans in Code, durch z.B. Compiler und Codegeneratoren.

- Fehlerhafte Bibliotheken-Inhalte.

Daneben können spezifische Fehlermodi der Werkzeuge beim Hardware-Entwurf auftreten:

- Fehlerhafte Umsetzung des generierten Codes in ein Chip-Layout.

- Fehlerhafte Übertragung (Programmierung) des erstellten Layouts in den Chip.

Ebenfalls ist der Faktor Mensch, als Entwickler oder Bediener, bei der Fehlerbetrachtung zu berücksichtigen, z.B. durch:

- Fehlerhafte Konzeption und Spezifikation vor dem Einsatz der Werkzeuge,

- Fehlerhafte Bedienung der Werkzeuge

Da im Lieferumfang der gängigen Entwicklungswerkzeuge in der Regel auch Prüf- bzw. Verifizierungswerkzeuge enthalten sind, sind auch Fehlermodi, die beim Testen des FPGA-Designs nicht erkannt werden, zu berücksichtigen.

- Fehlerhaftes Prüfwerkzeug

- Falsche Anwendung der Prüfwerkzeuge (Testprofil, Testfallgenerierung)

- Mangelnde Unabhängigkeit zwischen Entwicklungs- und Prüfwerkzeug

Dateiname: ISTec-A-4013\_A\_Bericht Rev.5.docx Seite 17 von 105

#### 3.3 Testen von FPGA-Designs

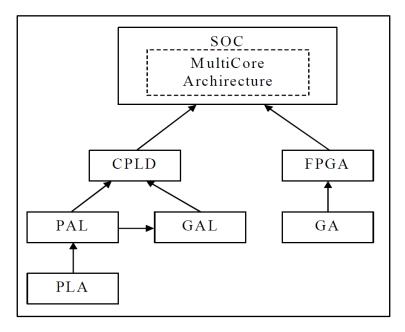

Für FPGA-Anwendungen, die Leittechnik-Funktionen der Kategorie A ausführen [11], sind die grundlegenden Qualifizierungsanforderungen und somit auch Testanforderungen in IEC 62566 Ed. 1 [4] festgelegt. Daneben sind Testanforderungen auch in IAEA-Publikationen [20], [21], [22] beschrieben und begründet. Abbildung 2 zeigt die Lebenszyklusphasen programmierbarer logischer Schaltungen gemäß IEC 62566 Ed. 1 [4]. Der Standard verwendet hierbei den Ausdruck HPD für Bausteine, die mittels einer Hardware-Beschreibungssprache (HDL) programmiert sind und in diesem Bericht als programmierbare logische Schaltungen bezeichnet werden.

Abbildung 2: Entwicklungslebenszyklus programmierbarer logischer Schaltungen (HPD) [4]

Für alle Entwicklungsphasen sind zur Gewährleistung sowie zum Nachweis der notwendigen Qualität eine unabhängige Verifizierung und Validierung durchzuführen und zu dokumentieren. In diesem Zusammenhang kommen Test-Werkzeuge, Test-Strategien und Test-Methoden zum Einsatz, die eine

- unabhängige Verifizierung der jeweiligen Lebenszyklusphase ermöglichen (korrekte Durchführung der Phasen),

- korrekte Ausführung des Entwicklungslebenszyklus validieren (gegen FPGA Anforderungen prüftechnisch bestätigen), und

- korrekte Ausführung phasenübergreifend und auf Systemebene validieren (gegen Systemanforderungen prüftechnisch bestätigen).

Die Anforderungsspezifikation bildet unter anderem Anforderungen an die Qualitätssicherung, relevante Entwicklungsstandards sowie lebenszyklusrelevante Anforderungen ab. Zudem gibt es dezidierte Anforderungen zu den internen und externen Schnittstellen, also den Bereichen, an denen die FPGA-Anwendung in ein bestehendes System eingebunden ist. Ein Test der Korrektheit dieser Anforderungen erfolgt in der Regel mittels Konfigurationswerkzeugen. Die Anforderungsspezifikation wird gemäß den kerntechnischen Regelwerksanforderungen mittels entwicklungsunabhängiger Testverfahren verifiziert. Insbesondere bei komplexeren FPGA-Designs kommen hierbei auch Prüfwerkzeuge, z.B. bei der Regelwerksumsetzung, Tests zur Konfiguration, Anforderungsverfolgung und Dokumentation zum Einsatz. Fehler oder

Dateiname: ISTec-A-4013\_A\_Bericht Rev.5.docx Seite 18 von 105

Mängel in der Anforderungsspezifikation wirken sich unmittelbar auf den kompletten Lebenszyklus der FPGA-Entwicklung aus. Ein besonderes Augenmerk gilt daher den Entwicklungswerkzeugen, die innerhalb eines Werkzeug-Sets schon in der frühen Phase der Entwicklung in die Prüfung der Spezifikation eingebunden sind.

Beim Entwurf wird die Konfiguration eines FPGA-Designs grafisch mittels eines Schaltplans oder textuell mit einer Hardwarebeschreibungssprache erstellt, welche die gesamte Funktion der Schaltung in Form von Strukturen und Abläufen beschreibt. Als Grundlage der Entwicklungswerkzeuge für FPGA-Designs haben sich Sprachen wie VHDL [23], Verilog [24] und SystemC [25] etabliert. Verilog gilt dabei neben VHDL als die meistgenutzte Hardwarebeschreibungssprache. Für die Entwurfserstellung kommen Werkzeuge wie z.B. LabVIEW [26] oder Matlab/Simulink [27] zum Einsatz, die über eine nutzerfreundliche graphische Oberfläche verfügen. Mit einem Synthesewerkzeug erstellt die verwendete Hardware-Beschreibung dann in mehreren Schritten für einen gewünschten Baustein eine spezifische Netzliste unter Nutzung der in diesem FPGA-Baustein verfügbaren Ressourcen. Die im Anschluss an die Hardware-Beschreibung durchzuführende Verifizierungsprüfung erfolgt in der Regel auch werkzeugbasiert (z.B. mittles ModelSim [28]).

Für das Testen von FPGA-Designs spielen neben den angewendeten Testmethoden vor allem auch die verwendeten Entwicklungswerkzeuge eine große Rolle. Hersteller und Lieferanten von FPGA-Technologien vermarkten in der Regel nicht nur die FPGA-Hardware, sondern zusätzlich auch Entwicklungs-, Test-, Simulations- und Verifizierungswerkzeuge. Diese Werkzeug-Sets werden jeweils in einem Entwicklungswerkzeug zusammengefasst. Als Beispiel werden für drei der auf dem kerntechnischen Markt etablierten FPGA Hersteller bzw. Lieferanten (Actel<sup>1</sup>, Altera<sup>2</sup>, Xilinx<sup>3</sup>) die jeweiligen Entwicklungswerkzeuge betrachtet.

Tabelle 4: Hersteller und Typen von FPGAs

| FPGA-Typ    | Hersteller/Lieferant        | Design-Werkzeug             |

|-------------|-----------------------------|-----------------------------|

| ACTEL [29]  | Actel GmbH;                 | IDE: Libero Integrated      |

|             | Dachorganisation: Microchip | Design Environment (IDE)    |

|             | Technology Inc.             | Microsemi [29]              |

| ALTERA [30] | ALTERA Cooperation;         | Quartus: Intel              |

|             | Dachorganisation INTEL      | "Quartus" FPGA Design       |

|             |                             | Software [30]               |

| XILINX [24] | Xilinx Cooperation          | Vivado: Vivado Design Suite |

|             |                             | [24]                        |

<sup>&</sup>lt;sup>1</sup> Der Bezug zum internationalen kerntechnischen Markt erfolgt über den FPGA-Hersteller Actel. Durch eine Übernahme ist Actel heute Teil der Microchip Technology Inc.

<sup>&</sup>lt;sup>2</sup> Der Bezug zum internationalen kerntechnischen Markt erfolgt über den FPGA-Hersteller Altera. Durch eine Übernahme ist Altera heute Teil von INTEL.

<sup>&</sup>lt;sup>3</sup> Der Bezug zum internationalen kerntechnischen Markt erfolgt über den FPGA-Hersteller XILINX. Durch eine Übernahme ist XILINX heute Teil von AMD.

- Libero ist laut Hersteller [29] ein speziell für Microsemi-FPGAs konzipiertes "Softwarewerkzeug-Set", welches die erforderlichen Werkzeuge für die Entwicklung, Evaluierung und Verifizierung der FPGA-Designs bereitstellt.

- Quartus [30] ist ein speziell für Intel® FPGAs konzipiertes "Softwarewerkzeug-Set", welches auch für CPLD eingesetzt wird und den gesamten FPGA Entwicklungsprozess einschließlich Synthese, Verifizierung und Simulation unterstützt.

- Vivado [24] wird von Xilinx als Input/Output Werkzeug-Set beschrieben, welches zur Entwicklung, Simulation, Platzierung ("place-and-route") und Synthese der FPGA-Designs eingesetzt wird. Darüber hinaus können spezielle Peripherien auf dem FPGA implementiert werden.

Gemäß IEC 62566 Ed. 1 [4] und IAEA NP-T-3.17 [21] sind Verifizierung und Validierung für HPD unabhängig von der Entwicklung durchzuführen. Dabei können z.B. folgende Testmethoden angewendet werden [15], [31], [32]:

- Statische Verifizierung: In IEC 62566 Ed. 1 [4] Kap 9.8 erfolgt hier eine Prüfung des Quellcodes nach vorher festgelegten Kriterien (typischerweise werkzeugbasiert).

- Zeitverhalten: Das Zeitverhalten (wie Signallaufzeiten und Verzögerungen) ist präzise bei den Simulationen nachzubilden, um eine Verifizierung auf Chipebene zu ermöglichen.

- Testbänke: In IEC 62566 Ed. 1 [4], Kap 9.5 sind Anforderungen an Testbänke für FPGA-Anwendungen festgelegt. Demnach sind unter anderem Simulation und Testprogramm (sog. Testbank) zu entwickeln und zu dokumentieren.

- Fehlerinjektion: In IAEA NP-T-3.17 [21] wird die Fehlerinjektion als Technik empfohlen, um die Testabdeckung weiter zu verbessern. Durch gezieltes Einbringen von Fehlern kann das Fehlerverhalten von FPGA-Anwendungen untersucht werden. Weitere Techniken sind Stress-Tests zur Prüfung von Anforderungen an die Robustheit sowie Untersuchungen im Zusammenhang mit Common Mode Analysen.

- Emulation: Durch Emulatoren werden, anders als bei einer Simulation, Teile von FPGA-Designs für Verifizierungszwecke ausschließlich funktional nachgebildet.

- Post-Route-Analysen: Diese Prüfmethoden werden in der Regel in Testbänken umgesetzt. Vor Implementierung des Design-Flows auf dem Chip wird in einer Simulationsumgebung das FPGA-Design detailgetreu nachgebildet, getestet und analysiert. Die so ermittelten Parameter, wie z.B. das Zeitverhalten, werden dann unter anderem zur Verifizierung der Korrektheit der tatsächlichen FPGA-Anwendung genutzt.

- Selbstüberwachung und Diagnosen: Diese sog. "online" Prüfmethoden, die sich auf die Robustheit der FPGA-Anwendung während ihres Betriebs auswirken, werden in der Regel über BIST realisiert. Sofern FPGA-Anwendungen in bestehende verteilte Leittechniksysteme integriert sind, werden zudem in der Regel die Selbstüberwachungsfunktionen des Leittechniksystems übergreifend auch für die FPGA-Anwendung genutzt. Anforderungen an die Nutzung von Selbstüberwachungen einschließlich BIST sind in IEC 62566 Ed. 1 [4], Kap. 6.4.9 festgelegt.

Dateiname: ISTec-A-4013\_A\_Bericht Rev.5.docx Seite 20 von 105

- Endlicher Zustandsautomat (engl.: finite state machine): Dieses Verifizierungsverfahren basiert auf einem Verhaltensmodell, bestehend aus Zuständen, Zustandsübergängen und Aktionen. Bei FPGA-Designs existieren dann je nach Komplexität Zustandsmatrizen, welche für eine endliche Anzahl an Zuständen die Kombinationen der jeweiligen Eingangs- und zugehörigen Ausgangsparameter abbilden. Dabei ist zu verifizieren, ob bei einer endlichen Zahl von Zuständen für sämtliche Kombinationen von Eingangsparametern der erwartete Zustand erreicht wird.

- Statische Laufzeit-Analyse (engl.: static timing analysis): Bei der statischen Laufzeit-Analyse wird eine Bewertung der tatsächlichen Signal-Laufzeit, ohne Nutzung einer Simulation des Schaltungsentwurfes, basierend auf Laufzeitberechnungen mittels kombinatorischer Logik, durchgeführt.

- Fehlerbeseitigungsprozess (engl.: fault resolution procedures): Gemäß IEC 62566 Ed.

1 [4] sind, übergeordnet zur Fehlerbeseitigung, die Prozesse von IEC 61513 Ed. 2 [12],

Kap. 6.3.2.4 anzuwenden. Die Anwendung dieser Prozesse soll sicherstellen, dass bei Modifikationen die Anforderungen von Kapitel 12 der IEC 62566 Ed. 1 [4] eingehalten werden.

- Software-FMEA (Failure Modes and Effects Analysis) für FPGAs [15]: Diese Analyse beruht auf der systematischen Betrachtung der Fehlermodi und ihrer möglichen Auswirkungen zur gezielten Ermittlung möglicher fehlervermeidenden bzw. fehlerbeherrschenden Maßnahmen.

Die nach IEC 62566 Ed. 1 [4] und IAEA NP-T-3.17 [21] vorgestellten Testmethoden haben sich bewährt. Unterstützt durch wiederkehrende Prüfungen sowie Selbstüberwachungs-Routinen kann für FPGA-Anwendungen eine hohe Verlässlichkeit erzielt werden [33], [34] und [35]. Die für die Umsetzung der Testmethoden eingesetzten Werkzeuge sind oftmals Bestandteil des Hersteller bereitgestellten Werkzeug-Sets. den vom Gemäß Regelwerksanforderungen sind die **Tests** unabhängig von den verwendeten Entwicklungswerkzeugen auszuführen. Somit muss beim Einsatz vorgefertigter Prüfwerkzeuge neben der Korrektheit des Prüfwerkzeugs ggf. auch die Unabhängigkeit der Prüfmethode vom verwendeten Entwicklungswerkzeug nachgewiesen werden.

#### 3.4 Vorangegangene eigene Projekte

Die Einführung und Weiterentwicklung immer komplexerer verfahrenstechnischer Systeme in den verschiedensten Bereichen führte auch in der Kerntechnik zu einer erhöhten Verwendung programmierbarer digitaler Leittechniksysteme mit sicherheitstechnischer Bedeutung. Die Frage nach einer Quantifizierung der Zuverlässigkeit dieser Systeme mithilfe eines allgemein anerkannten Verfahrens ist dabei noch nicht abschließend geklärt. Es gibt eine Reihe von Ansätzen, die meist Teilprobleme behandeln [6]. Die Ergebnisse der bisherigen Forschungsvorhaben [5], [7], [13], [14] und [9] leisten ebenfalls einen Beitrag zur Quantifizierung von Zuverlässigkeitseigenschaften auf der Basis von Komplexitätsberechnungen. Die Komplexitätsbewertung ist umso gebotener, da das deutsche kerntechnische Regelwerk neben Anforderungen zur Zuverlässigkeit auch Anforderungen an die Begrenzung der Komplexität von Sicherheitsleittechnik enthält [10].

Wie die praktische Erfahrung zeigt, ist es die Komplexität eines programmierbaren digitalen Systems in Verbindung mit der Vielfalt der Anwendungsprofile, wovon das Risiko einer Fehlfunktion des Systems entscheidend abhängt. Deshalb stellt sowohl die Bestimmung der Komplexität der Software bzw. der programmierbaren Logik als auch der Ansatz, die Zuverlässigkeit programmierbarer digitaler Leittechniksysteme auf der Grundlage der Komplexität der Software bzw. der programmierbaren Logik zu bewerten, eine wichtige Zielsetzung dar. Eine Methode zur Messung der Komplexität, die sich auf ein strukturiertes Vorgehen stützt, wurde in im Rahmen eines vorangegangenen Forschungsvorhabens [5] für eine spezifische CPU-basierte Leittechnikplattform entwickelt. Um das entwickelte Konzept für verschiedene digitale Leittechniksysteme verwendbar zu gestalten, wurde die Methodik im Rahmen des letzten Forschungsvorhabens [9] sowohl für CPU-basierte Anwendungen weiterentwickelt als auch für FPGA-basierte Anwendungen nutzbar gemacht.

Für die Komplexitätsbewertung wurde in [5] ein Verflechtungsmaß definiert, welches auf der Verschaltung der Logik eines Programms basiert. Neben dem Verflechtungsmaß werden Komplexitätsaspekte herangezogen und zu einem Komplexitätsvektor zusammengefasst, der als Ausgangspunkt für die Bewertung und Ableitung von Zuverlässigkeitsaussagen dient. Die Berechnung des Verflechtungsmaßes basiert in [5] auf der Verschaltung von Funktionsbausteinen und Eingabe-Signalen eines Funktionsplans. Dabei können einzelne Funktionsbausteine oder auch ganze Sätze von Funktionsbausteinen zur Berechnung von mehr als nur einem Ausgangssignal verwendet werden. Diese Verflechtung V(FP) hinsichtlich der Berechnung verschiedener Ausgangssignale ist kennzeichnend für die Komplexität eines Funktionsplans. Eine weitere wesentliche Rolle spielt die Verflechtung, die durch die Verwendung gemeinsamer Eingangssignale gegeben ist.

Die Menge der Funktionsbausteine, die zur Berechnung eines Ausgangssignals S beitragen, bilden den Vorbereich VB(S) des Ausgabesignals S.

Die Menge der Eingangssignale, die zur Bildung des Ausgangssignals S verwendet werden, bilden den Input IN(S) des Ausgangssignals S.

Die Verflechtung V (FP) eines Funktionsplans ist definiert durch

$$V(FP) = \sum_{i} \frac{|VB_{FB}(S_{Ai})| + |IN(S_{Ai})|}{|BFP| + |SIN|}$$

(1)

Dateiname: ISTec-A-4013\_A\_Bericht Rev.5.docx Seite 22 von 105

Diese Größe hängt von der Verflechtung der Vorbereiche VB(S) und der Inputs IN(S) aller Ausgangssignale eines Funktionsplans ab.

Dabei bezeichnet:

S<sub>Ai</sub> die einzelnen Ausgangssignale des Funktionsplans FP

$VB_{FB}(S_{Ai})$  die Menge der Funktionsbausteine, die zur Berechnung des Ausgangsignals  $S_{Ai}$  beitragen

$\mathsf{IN}(\mathsf{S}_{\mathsf{A}\mathsf{i}})$  die Menge der Eingang-Signale, die zur Berechnung des Ausgangssignals  $\mathsf{S}_{\mathsf{A}\mathsf{i}}$  beitragen

BFP die Menge der Funktionsbausteine, aus denen der Funktionsplan FP besteht

SIN die Menge der Eingangssignale des Funktionsplans FP

I I die Mächtigkeit (Anzahl der Elemente) einer Menge

Mit den erarbeiteten Komplexitätsmaßen und dem daraus resultierenden Komplexitätsvektor wurde Software betrachtet, die z.B. bei CPU-basierten Anwendungen zum Einsatz kommt. Die Erweiterung der Methodik auf FPGA-basierte Anwendungen erfolgte in [9]. Dafür wurden zusätzliche Komplexitätsmaße zur Bewertung hinzugezogen und der Komplexitätsvektor entsprechend erweitert und anschließend für die Anwendung auf FPGA-basierte Anwendungen modifiziert. Der aktuelle Stand dieser Bewertungsgrößen, die als Grundlage für die Komplexitätsbewertung in dem laufenden Vorhaben herangezogen werden, ist in Tabelle 5 dargestellt.

Das zur Komplexitätsbewertung definierte Verflechtungsmaß (1) der Funktionspläne wurde um ein modifiziertes (2) und internes Verflechtungsmaß (3) erweitert, um eine höhere Aussagekraft der Messung der Komplexität zu erzielen. Das modifizierte Verflechtungsmaß  $V_{mod}(FP)$  spiegelt die interne Verknüpfung einer Schaltung stärker wider.

$$V_{mod}(FP) = \sum_{i} \frac{|VB_{FB}(S_i)| + |IN(S_i)|}{|BFP| + |SIN|}$$

(2)

Die Verflechtung wird bei diesem Maß über die Vorbereiche und die zur Berechnung herangezogenen Eingangssignale der internen Signale  $S_i$  berechnet. Hierbei steht  $S_i$  für alle Signale (Ausgabesignale und internen Signale) des Funktionsplans. Somit stellt  $VB_{FB}(S_i)$  die Menge der Funktionsbausteine, die zur Berechnung der Ausgabesignale bzw. der internen Signale beitragen, dar.

Bildet man die Differenz

$$V_{intern}(FP) = V_{mod}(FP) - V(FP) \ge 0$$

(3)

ergibt sich eine Maßzahl V<sub>intern</sub>(FP), die unabhängig von der Anzahl der Ausgangssignale ist. Diese Zahl kann als eine Charakteristik der inneren Komplexität des Funktionsplans

Dateiname: ISTec-A-4013\_A\_Bericht Rev.5.docx Seite 23 von 105

verstanden werden. Diese Differenz ist immer größer oder gleich Null, da  $V_{mod}(FP)$  immer größer oder gleich V(FP) ist.

Berechnung des Verflechtungsmaßes basiert auf der Verschaltung der Funktionsbausteine bzw. Basisblöcke und der Eingangssignale des Funktionsplans bzw. der Netzliste, und ist sowohl auf Funktionspläne CPU-basierter Anwendungen als auch auf Netzlisten von FPGA-basierten Anwendungen anwendbar. Neben den Verflechtungsmaßen werden weitere Komplexitätscharakteristiken wie Anzahl der Ein- und Ausgangssignale, Anzahl der Bausteine bzw. Blöcke eines Funktionsplans bzw. einer Netzliste, Anzahl der Verbindungen sowie vor- und nachgelagerte Funktionspläne bzw. Netzlisten berücksichtigt. Aus verschiedenen Komplexitätscharakteristiken wurde ein modifizierter Komplexitätsvektor gebildet, der auf FPGA-basierte Anwendungen anwendbar ist. Der Komplexitätsvektor ist Ausgangspunkt für die Ableitung von Kriterien zur Bewertung der Zuverlässigkeit digitaler Leittechniksysteme.